先进封装方向:SiP、3D、MEMS 等。封装的本质是电气互连,在芯片小型化和高效率的需求驱动下,SiP 封装、3D 封装、MEMS 封装等新型工艺将是全球半IC封装产业的可以发展方向。

先进封装的发展方向是“以点替代线的连接”,完成“点的连接”的核心工艺是 TSV 和 Bumping(Copper Pillar):

封装技术更新的驱动力是使封装器件微型化、低成本和高性能,从芯片互连技术角度看,封装技术发展路径是,第一代WB技术,第二代TAB技术,第三代FC技术,第四代TSV技术,这是电气连接技术“点替代线”思路的体现;

引线键合是空间操作,点对点连接是平面操作,点代替线可以使连接电路的空间分布更加简单,从而减小封装体积;点替代线可以充分利用芯片的自身面积,可以减小封装面积,实现微型化;

此外,Bumping 技术是可以批量生产的,而键合技术如 WB 或者 TAB 只能对单个芯片操作,因此点替代线可以实现晶圆级封装WLP,从而大大减少封装成本;

点对点连接,可以缩短连接电路长度,减少系统寄生电容干扰、电阻发热和信号延迟,提高模组性能。

参考观研天下发布《2018-2023年中国集成电路封装行业市场发展现状调查及投资前景规划预测报告》

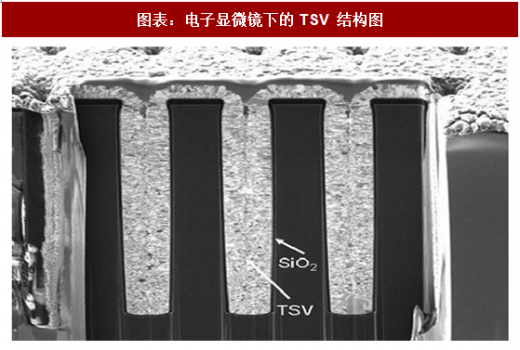

TSV(Through Silicon Via,硅通孔)工艺简介:通过在晶粒内部打垂直通孔并填充金属(Cu/W),将晶粒正面焊盘上的 I/O 信号引至背面,从而实现3D IC内部各层晶粒间的垂直互连,是SiP/3D封装中的关键工序。

TSV制造工艺包括通孔制造,绝缘层、阻挡层制备,通孔金属化,芯片减薄,技术难度远大于传统Wire Bonding技术;TSV 技术是实现相邻晶粒间垂直互连的最短连接方式,可降低芯片功耗,提高运行速度。

从纵向看,TSV将晶粒的电气连接端口限制在一个“点”(Wire Bonding 则需用“线”将端口引出),减小了3D IC的水平面积,同时TSV实现晶粒垂直互连不需要像Package on Package等3D封装使用基板,减少了芯片厚度,从而使芯片的三维封装密度达到最大;

Bumping 技术简介:通过在芯片表面制作金属凸块提供芯片电气互连的“点”接口,反应了先进制程以“点替代线”的发展趋势,广泛应用于FC、WLP、CSP、3D等先进封装。它提供了芯片之间、芯片和基板之间的“点连接”,由于避免了传统Wire Bonding向四周辐射的金属“线连接”,减小了芯片面积(封装效率 100%),此外凸块阵列在芯片表面,引脚密度可以做得很高,便于满足芯片性能提升的需求;

从工艺来看,加工时首先在晶圆上生长钝化层,然后用Ti/Ni在其上制作金属层 UBM,最后利用焊接/电镀在 UBM上生长出铅锡合金球/金球形成Bumping;Copper Pillar 是 Bumping 互连技术中最先进的一种,用铜柱替换金属球作为芯片表面的电气接口,由于相邻铜柱轴间距很小(目前Amkor为50微米),因而I/O引脚密度可以做的更高,芯片尺寸可进一步缩小。

【版权提示】观研报告网倡导尊重与保护知识产权。未经许可,任何人不得复制、转载、或以其他方式使用本网站的内容。如发现本站文章存在版权问题,烦请提供版权疑问、身份证明、版权证明、联系方式等发邮件至kf@chinabaogao.com,我们将及时沟通与处理。